# Concurrent Multiband Low-Noise Amplifiers—Theory, Design, and Applications

Hossein Hashemi, *Student Member, IEEE*, and Ali Hajimiri, *Member, IEEE*

*Invited Paper*

**Abstract**—The concept of *concurrent multiband low-noise-amplifiers* (LNAs) is introduced. A systematic way to design concurrent multiband integrated LNAs in general is developed. Applications of concurrent multiband LNAs in concurrent multiband receivers together with receiver architecture are discussed. Experimental results of a dual-band LNA implemented in a 0.35- $\mu$ m CMOS technology as a demonstration of the concept and theory is presented.

**Index Terms**—Amplifier noise, land mobile radio cellular systems, low-noise amplifier, radio communication, radio receivers.

## I. INTRODUCTION

**S**TANDARD receiver architectures, such as superheterodyne and direct conversion, accomplish high selectivity and sensitivity by narrow-band operation at a single input frequency [1]. These modes of operation limit the system's available bandwidth and robustness to channel variations and thus its functionality. On the other hand, wide-band modes of operation are more sensitive to out-of-band unwanted signals (blockers) due to transistor nonlinearity. These out-of-band blockers can severely degrade receiver's sensitivity.

The diverse range of modern wireless applications necessitates communication systems with more bandwidth and flexibility. More recently, dual-band transceivers have been introduced to increase the functionality of such communication systems by switching between two different bands to receive *one band at a time* [2]–[5]. While switching between bands improves the receiver's versatility (e.g., in multiband cellular phones), it is not sufficient in the case of a multifunctionality transceiver where more than one band needs to be received simultaneously (e.g., a multiband cellular phone with a global positioning system, global position system (GPS), receiver and a Bluetooth interface). Using conventional receiver architectures, simultaneous operation at different frequency bands can only be achieved by building multiple independent signal paths with an inevitable increase in the cost, footprint, and power dissipation. Although there have been efforts to minimize the number of additional

Manuscript received May 28, 2001. This work was supported by Conexant Systems and by NSF-ERC.

The authors are with the Caltech High-Speed Integrated Circuits Group, Electrical Engineering Department, California Institute of Technology, Pasadena, CA 91125-9300 USA (e-mail: hashemi@caltech.edu; hajimiri@caltech.edu).

Publisher Item Identifier S 0018-9480(02)00843-8.

components used for the second band of operation (e.g., for adding GPS to a CDMA phone [6]), none of these efforts attempt simultaneous reception of more than one band.

In this work, a new *concurrent dual-band receiver architecture* is introduced that is capable of simultaneous operation at two-different frequencies without dissipating twice as much power or a significant increase in cost and footprint [7]. This concurrent operation can be used to extend the available bandwidth, provide new functionality, and/or add diversity to battle channel fading. The concurrent operation is realized through an elaborate frequency conversion scheme in conjunction with a novel concurrent dual-band low-noise amplifier (LNA). These new concurrent multiband LNAs provide simultaneous narrow-band input matching and gain at multiple frequency bands, while maintaining low noise.

Section II reviews the current advances of single-band LNAs from technological and architectural points of view. Section III briefly describes one such receiver architecture demonstrating the central role of the concurrent LNAs in the receiver. The general design methodology of concurrent multiband LNAs is discussed in Section IV. Experimental results of a concurrent dual-band CMOS LNA will be presented in Section V.

## II. A REVIEW OF SINGLE-BAND LNA DESIGN ISSUES

Being the first active element in the receiver chain, the noise figure (NF) of an LNA plays a significant role in the overall NF of the receiver, which controls its sensitivity and output signal-to-noise ratio (SNR) [8]. Before exploring the design details of concurrent multiband LNAs, it is helpful to review some of the existing technological and topological choices for single-band LNAs.

### A. Technology

The bipolar junction transistor was the first solid-state active device to provide practical gain and NF at microwave frequencies [9]. In the seventies, breakthroughs in the development of field-effect transistors (FETs) (e.g., GaAs MESFET) led to higher gain and lower NF than bipolar transistors for the frequencies in the range of several gigahertz [10]. Currently, advanced FETs and bipolar transistors still compete for lower NF and higher gain at frequencies in excess of 100 GHz.

Examples are the high electron-mobility transistors (HEMTs), such as pseudomorphic high electron-mobility transistors (pHEMTs) [11], metamorphic high electron-mobility transistors (MHEMTs) [12], as well as heterojunction bipolar transistors (HBTs) [13], [14], built using a variety of semiconductor materials (e.g., GaAs, InP, Si, SiGe).

Traditionally, very low-noise amplifiers at high frequencies have been made using transistors with high electron mobility and high saturation velocity on high-resistivity substrates for the following principal reasons.

- 1) Higher carrier mobility and peak drift velocity result in a higher transistor transconductance and shorter carrier transit time [10] for a given current, thus allowing for the reduction of the dc current for the same transconductance (gain) in transistors which lowers the input-referred noise and, hence, the NF. This gives compound semiconductors a significant advantage over silicon, as for instance, the electron mobility and the peak drift velocity are typically six and two times larger, respectively, for GaAs when compared to silicon [10].

- 2) Higher carrier mobility also results in lower parasitic drain and source series resistors. The parasitic source resistance can be a major contributor to the overall NF of certain LNAs, such as those used for satellite communications.

- 3) Due to mostly technological limitations, the series input resistance of silicon-based transistors is usually higher than those of compound semiconductors. In particular, the lower resistance of the metal gate of GaAs MESFETs compared to higher resistance of the poly-silicon gate in MOSFETs and thin bases in bipolar transistors, result in a lower NF for GaAs transistors.

- 4) The loss properties of on-chip passive components can have a significant effect on the noise and gain performance of the LNAs. High-resistivity substrates minimize the substrate loss components. As the loss and noise are closely related through the fluctuation-dissipation theorem of statistical physics [15], [16], the energy loss reduction translates to a lower NF for the amplifier.

Despite the above mentioned limitations of silicon technologies, several silicon LNAs have been reported. Meyer *et al.* reported one of the early LNAs made on a low-resistivity (i.e., lossy) silicon substrate using bipolar junction transistors for commercial cellular applications [17], where very low NF is not needed. Recently, a large number of efforts have been reported to use the advanced digital CMOS processes for single-chip implementation of the complete radio transceiver [18], [19]. Significant progress in CMOS LNA design has been made during the last several years where more recent results, such as [20], demonstrate significant improvements over the earlier works [21]–[23] and show that CMOS LNAs can be a worthy competitor for compound semiconductor implementations in many portable applications.

### B. Topology

Although several different topologies have been proposed to implement LNAs, we will only focus on two most

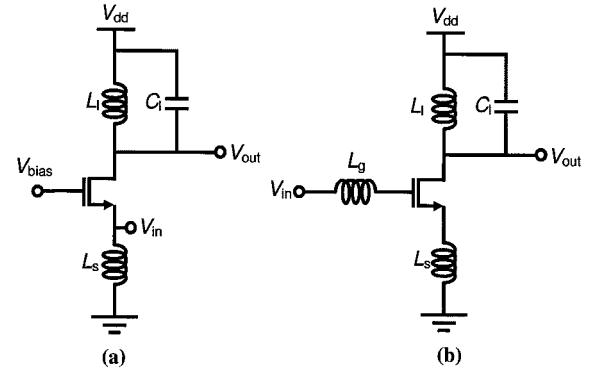

Fig. 1. Commonly used single-band CMOS LNAs. (a) Common-gate. (b) Common-source with inductive degeneration.

common single-stage<sup>1</sup> LNAs in CMOS processes, namely, the common-gate topology [22] and inductively degenerated common-source stage [23], [24], shown in Fig. 1.

The common-gate configuration uses the resistive part looking into the source of the transistor to match the input to a well-defined source impedance (e.g.,  $50\ \Omega$ ). This impedance is  $1/(g_m + g_{mb})$  in the case of a MOSFET, where  $g_m$  and  $g_{mb}$  are transconductances of the top-gate and back-gate transistors, respectively. However, it can be shown that the NF is lower bounded to 2.2 dB for a perfectly matched long-channel CMOS transistor [22] unless a transformer is used at the input [25].

In a common-source LNA, inductive degeneration is used to generate the real part needed to match the LNA input to the preceding antenna or filter. Strutt and Van der Ziel first noticed that inductive degeneration can enhance the output SNR [26]. The ideal lossless inductive feedback moves the source impedance for optimum NF toward the optimum power match with a minor increase in the minimum NF [27]. Unfortunately, in silicon implementations, the loss associated with inductors will degrade the NF. It should be mentioned that in these cases cascode configuration can be used to enhance the stability and reverse-isolation of the amplifier.

While the problem of achieving the lowest noise in an amplifier has been solved for a general case through a mathematical treatment [28], this general approach still does not provide the necessary insights into the design.

An alternative approach is to use Smith charts to find the optimum impedance for noise and power matching at the input of the amplifier for given active device [29]–[31]. Although the Smith chart is a very convenient tool for seeing how close we are to the minimum NF and the maximum gain of a given device, it does not show the effect of individual noise sources on the total NF. This is particularly important for a concurrent multiband LNA, since different noise sources behave differently at different frequencies.

Unlike bipolar transistors whose dc current sets the transconductance and minimum noise-figure, MOSFETs offer extra degrees of freedom in choosing the device width and length. These extra degrees of freedom can be used to improve the NF and the gain of the amplifier. Recently, some work has been done to calculate and minimize the NF of a single-band common-source

<sup>1</sup>This discussion is also valid for the first stage of multistage LNAs.

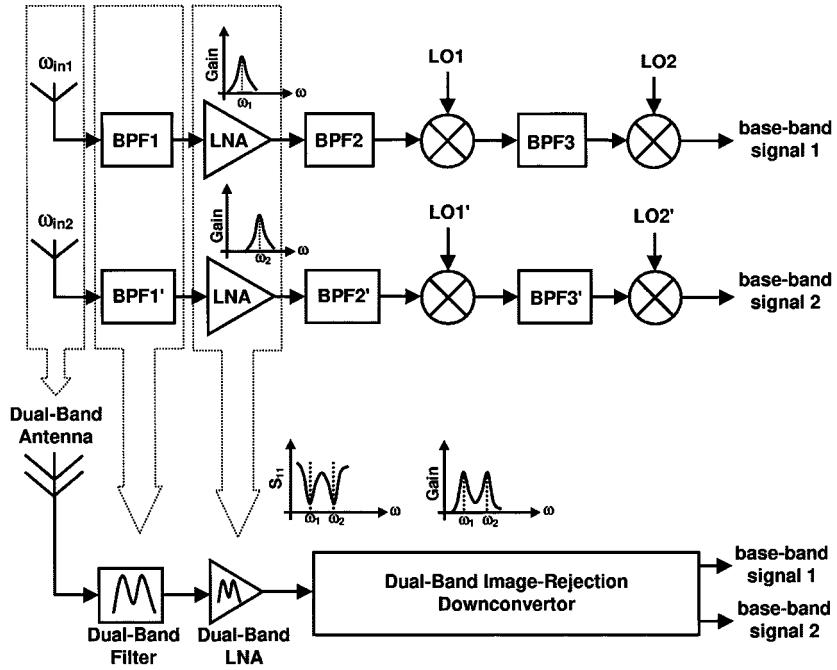

Fig. 2. Evolution process of two parallel receivers to a concurrent dual-band receiver.

CMOS LNA with inductive degeneration using a more systematic approach [23]. In the next section, we will introduce the concept of a concurrent receiver and a new architecture to implement it. In Section IV, we present a general approach for the design of concurrent multiband LNAs which are important building blocks in concurrent receivers.

### III. CONCURRENT RECEIVER ARCHITECTURES

In this section, we will develop a concurrent dual-band receiver architecture that can be fully integrated. The objective is to devise a receiver that can simultaneously receive signals at two different frequency bands with maximum reuse of power and building blocks.

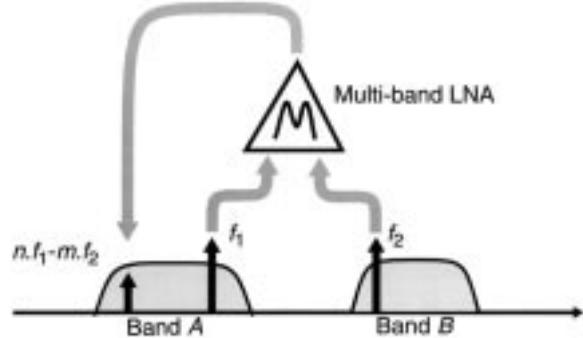

Fig. 2 shows the conceptual evolution of a dual-band receiver, starting with two totally independent heterodyne receiving paths, and leading to an efficient concurrent dual-band receiver.

The first gain stage in a concurrent dual-band receiver is its LNA. Traditional single-band LNAs use a single or cascode transistor stage to provide wide-band transconductance and combine it with proper passive resonant circuitry at the input and output as discussed briefly in the previous section. This approach shapes the frequency response, ensures stability, and achieves gain and matching at the single band of interest [31].

A very important observation is that the transconductance of the transistor is inherently wide-band and can be used to provide gain and matching at other frequencies without any penalty in the power dissipation. This observation leads to a compact and efficient front-end for a concurrent dual-band receiver which consists of a dual-band antenna [32]–[34], followed by a monolithic dual-band filter [35] and a concurrent dual-band LNA that provides simultaneous gain and matching at two bands, as shown at the bottom of Fig. 2. A detailed approach to the design of such a multiband LNA will be described in the subsequent sections. It should be noted that the concurrent dual-band

Fig. 3. An architecture for concurrent dual-band receiver.

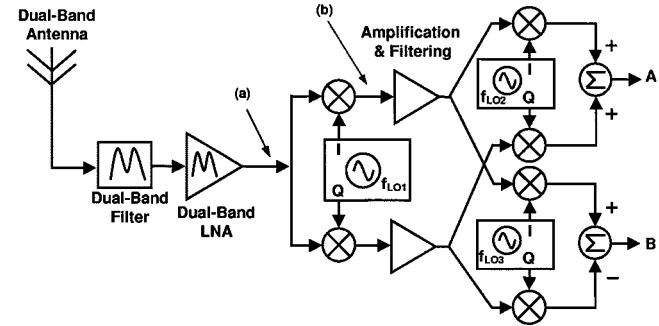

receiver does not need any dual-band switch [36] or diplexer [37], because simultaneous reception at both bands is desired. Then a dual-band down-conversion scheme is needed to translate different information carrying signals to baseband with as few local oscillators (LOs) and external filters as possible, while maintaining isolation between the two bands. This can be done in many different ways, for instance, Fig. 3 shows a simplified block diagram of one such receiver.

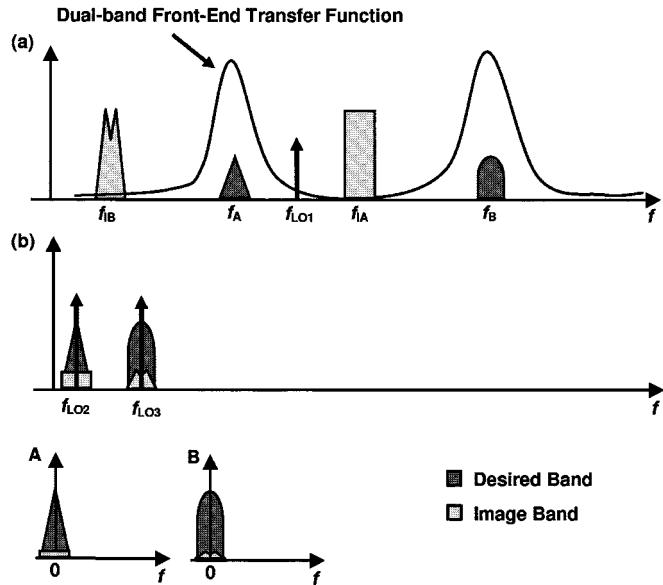

The frequency of the first LO that appears after the LNA and performs the first down conversion determines the image frequency(ies) and plays an important role in the performance of the system. For a *nonconcurrent* receiver, it has been proposed to choose the first LO frequency halfway between the two frequency bands and select the band of interest by choosing the appropriate sideband produced by an image-separation mixer [2]. Although this method is sufficient for the nonconcurrent approaches, it will suffer from some serious shortcomings if used for a *concurrent* receiver, where the LNA amplifies the signal in both of the desired bands. This is because one band is the image of the other and there is no attenuation of the image by either the antenna or the filter. The situation is exacerbated by the LNA

Fig. 4. Frequency-domain signal evolution in the concurrent dual-band receiver of Fig. 3.

gain in the image band. In this scenario, one is solely relying on the image rejection of the single sideband receiver, which is limited by the phase and amplitude mismatch of the quadrature LOs and the signal paths [38], [39], and is insufficient in a concurrent receiver.

An alternative approach that does not suffer from the above problem and, in fact, significantly improves the image rejection is to use an offset LO as shown in Fig. 4. The LO frequency is offset from the midpoint of the two bands of interest ( $f_A$  and  $f_B$ ) in such a way that the image of the first band at  $f_A$  falls at the notch of the front-end transfer function at  $f_{IA}$ . The attenuation at  $f_{IA}$  is determined by the compounded attenuation of the dual-band antenna, filter, and LNA. Similarly, the image of the second band at  $f_B$  will fall outside the passband of the front-end at  $f_{IB}$  and will be attenuated, accordingly. Using a quadrature first LO makes the stage fit to act as the first half of any single-sideband image-reject architecture, such as that proposed by Weaver [40]. Since the receiver has to demodulate two bands concurrently and independently, two separate paths *must* be used eventually. Each path comprises the second half of the image reject architecture, as shown in Fig. 3, which provides further image rejection (Fig. 4). This architecture eliminates an extra antenna, a front-end filter, an LNA, and a pair of high-frequency mixers, which in turn results in power, footprint, and area savings. At the same time, large image rejection in excess of that of the single-sideband receiver is achieved through diligent frequency planning and proper usage of stop-band attenuation.

#### IV. CONCURRENT MULTIBAND LNA

In a single-band LNA, passive networks are used to shape the response of the wide-band transconductance of the active device in the frequency domain to achieve gain and matching at the frequency of interest. This concept can be generalized to multiple frequency bands noting that the intrinsic transconductance of the active device is inherently wide-band and can be used at multiple frequencies simultaneously.

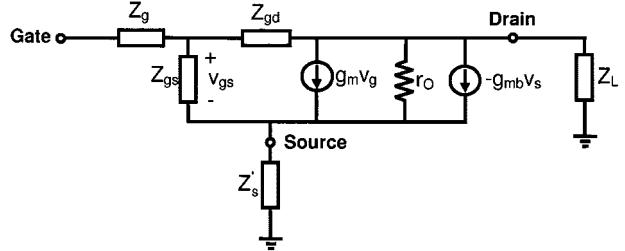

Fig. 5. General model for a single-stage amplifier in common-source configuration.

It is crucial to note the fundamental differences between the concurrent and the existing nonconcurrent approaches. In conventional dual-band LNAs, either one of the two single-band LNAs is selected according to the instantaneous band of operation [41], [42], or two (three) single-band LNAs are designed to work in parallel using two (three) separate input matching circuits and two (three) separate resonant loads [2], [43]. The former approach is nonconcurrent, while the latter consumes twice (three times) as much power if used in a concurrent setting. The other existing approach is to use a wide-band amplifier in the front-end [44]. Unfortunately, in a wide-band LNA, strong unwanted blockers are amplified together with the desired frequency bands and significantly degrade the receiver sensitivity.

In this section, we present an analytical approach to the design of a general class of integrated concurrent multiband LNAs. The concurrent LNA is proposed as a solution to the aforementioned problems in a concurrent receiver.

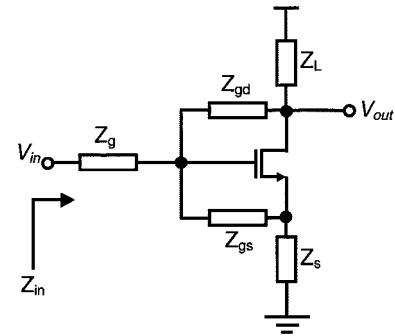

##### A. General Amplifier in Common-Source Configuration

In this section, we use a general model for an amplifier in the common-source configuration to obtain an equivalent circuit for the input impedance and a general expression for the gain at multiple frequencies. This equivalent circuit will be used to achieve simultaneous power and noise matching in a concurrent multiband LNA. Fig. 5 shows a transistor<sup>2</sup> with arbitrary gate impedance  $Z_g$ , gate-source impedance  $Z_{gs}$ , source impedance  $Z_s$ , gate-drain impedance  $Z_{gd}$ , and load impedance  $Z_L$ . The impedances shown in Fig. 5 also include the transistor's inherent passive components (e.g.,  $C_{gs}$ ,  $C_{gd}$ ). General expressions for input impedance and voltage-gain of this amplifier are found in Appendix A.

##### B. Input Matching

The input of the LNA is either fed directly by the antenna or is connected to the antenna through a bandpass filter, a diplexer/duplexer, or both. In any case, the impedance looking into the input of the LNA should be power matched (i.e., complex conjugate matched)<sup>3</sup> to the impedance of the preceding stage for maximum signal power transfer. Additionally, it is

<sup>2</sup>While the general active device discussed here is a MOS transistor, a similar analysis applies to other active devices (e.g., BJT, MESFET.)

<sup>3</sup>In large-signal devices, power match does not necessarily correspond to the complex conjugate matching. However, since the LNA design is based on small-signal principals, we can use two terms, synonymously.

Fig. 6. General representation of any (a) noisy two-port and (b) its equivalent circuit.

essential to provide the correct impedance to the preceding stage to satisfy its nominal specifications (e.g., bandpass filter characteristics, such as rolloff, etc., depend on filter loading).

The expressions in Appendix A can be further simplified if we assume that  $Z_{gd}$  is much larger than the other impedances. This assumption neglects the effect of the transistor's intrinsic  $C_{gd}$  and its associated Miller effect. Then, the input impedance expression of (21) simplifies to

$$Z_{in} = Z_g + Z_{gs} + Z'_s(1 + g_m Z_{gs}). \quad (1)$$

This expression will be used in the following section to design multiband input matching networks.

Theoretically, the input impedance of any stable amplifier with a nonzero real part can be perfectly matched to any arbitrary source impedance (with a positive real part) for a single frequency using lossless passive components at the input of the amplifier [45]. Equation (1) can be used to generalize this *power match* concept to multiple frequencies. It can be used to generate numerous topologies to achieve simultaneous impedance matching at multiple distinct frequencies.

In an LNA, it is also necessary to achieve a *noise match* at the input for the frequency(ies) of interest to minimize the NF. In the following section on noise matching, we will demonstrate that one way to minimize the NF of the amplifier of Fig. 5 is by designing the passive network so that it satisfies  $Z_g + Z_{gs} + Z'_s = 0$  at multiple frequencies of interest. However, this can only be achieved using lossless passive components. Therefore, in practice, one should minimize  $Z_g + Z_{gs} + Z'_s$ , to its smallest real part,  $R_{min}$ . Having satisfied the above condition, the input impedance will be

$$Z_{in} = g_m Z_{gs} Z'_s + R_{min}. \quad (2)$$

Theoretically, a large number of passive topologies for  $Z_{gs}$  and  $Z'_s$  can provide input impedance matching at multiple frequency bands. One particular example which is of great practical value is when  $Z_{gs}$  is just the intrinsic gate-source capacitance,  $C_{gs}$  and, hence,  $Z'_s$  has to be an inductor as in the single-band common-source LNA in [26], [24], [23]. For negligible passive loss ( $R_{min} \approx 0$ ) and a real-value impedance  $Z_{in}$ ,  $R_{in}$  (e.g.,  $50 \Omega$  for most practical cases), the source inductor is given by

$$L_s = \frac{R_{in} C_{gs}}{g_m} \approx \frac{R_{in}}{\omega_T}. \quad (3)$$

This will result in a passive network for  $Z_g$  that will minimize  $Z_g + Z_{gs} + Z'_s$  for all the frequencies of interest. One example of such a design can be found in Section V.

The optimum source inductance depends on  $\omega_T$  and, hence, process parameters, as (3) suggests. Ignoring  $C_{gd}$ , in a deep short-channel CMOS biased in the velocity saturation region,  $\omega_T$  is approximately given by

$$\omega_T \cong \frac{g_m}{C_{gs}} = \frac{3}{4} \mu_n \frac{E_C}{L} = \frac{3}{4} \cdot \frac{v_{sat}}{L} \quad (4)$$

where  $\mu_n$  is electron mobility in the channel,  $E_C$  is the critical field,  $v_{sat}$  is the saturation velocity, and  $L$  is transistor's channel length. Therefore, for a given deep submicrometer CMOS technology with constant channel length where carriers are velocity saturated, the value of  $L_s$  is almost fixed and is independent of the bias current and the device size. For a bipolar transistor,  $\omega_T$  has a current dependency. However, if junction capacitors are negligible for a transistor biased with a high collector current, this current dependency is small and again the value of  $L_s$  is independent of bias current. In a long-channel CMOS,  $\omega_T$  depends on the bias current and the device width and so will  $L_s$ .

### C. Noise Matching

An important design parameter in receiver design, which is the measure of receiver noise, is the noise factor  $F$  (also known as NF, when expressed in decibels). The definition of the noise factor of any transducer (e.g., LNA, mixer, filter, etc.) given by [46] is

$$F = \frac{N_{total}}{N_{source}} \quad (5)$$

where  $N_{total}$  is the total noise power per unit bandwidth available at the output port<sup>4</sup> at a corresponding output frequency when the noise temperature of its input termination is a standard 290 K at all frequencies and  $N_{source}$  is that portion of  $N_{total}$  engendered at the input frequency by the input termination at the standard noise temperature<sup>5</sup> 290 K.

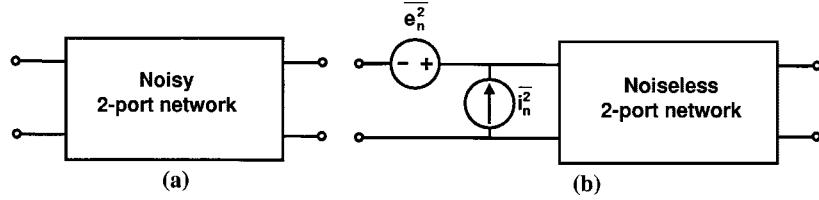

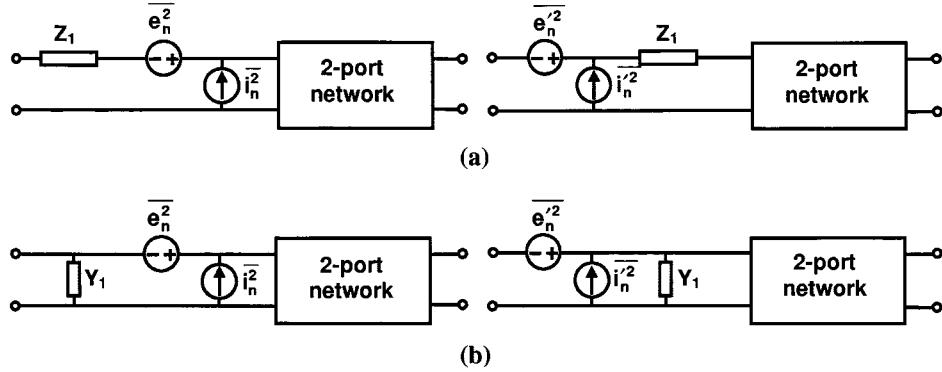

Any noisy two-port network can be represented by a noiseless two-port network with input equivalent voltage  $e_n$  and current

<sup>4</sup>Actually, noises can be referred to any other node, e.g., input node, in the circuit.

<sup>5</sup>While the NF is a useful parameter in practice, it is an incomplete measure of an LNA's performance, as it is desirable to have a low NF while maintaining a high gain. For example, feedback can be used to reduce  $F$  as close to unity as possible, at the price of lowering the gain in the process [28], [47]. Cascading multiple stages of such feedback amplifiers to recover the original gain will result in a noise factor larger than or equal to the noise factor of the original amplifier without feedback [48]. A more accurate measure of an amplifiers noise performance, called the noise measure  $M$  is defined in [28] to take the effects of both gain and NF into account.

sources  $i_n$ , [49], as shown in Fig. 6. Then, the noise-factor  $F$  will be given by

$$F = \frac{\overline{i_s^2} + \overline{|i_n + Y_s c_n|^2}}{\overline{i_s^2}} \quad (6)$$

where  $Y_s$  is the reference source admittance (e.g.,  $Y_s = 1/50 \Omega$ ) for the NF and  $i_s$  is the noise current associated with it.

In general, equivalent input voltage and current sources are correlated. The effect of adding components in series or parallel to the input of the network on the equivalent input voltage and current noise sources can be easily modeled by the *noise-source transformations* (Appendix B).

Now, we will find an expression for the NF of the general single-stage common-source amplifier of Fig. 5. While it is possible to include all the different noise sources in the calculations, we will make certain simplifying assumptions to keep the expressions tractable. In the following calculations, we assume that the only dominant noise sources are the drain and gate-induced current source  $i_{nd}$  and  $i_{ng}$  [50] for the MOS transistor and collector and base shot noise currents  $i_{nc}$  and  $i_{nb}$  for the bipolar transistor. It is also assumed that passive impedances shown in Fig. 5 do not contribute any noise. The noise of any physical input resistance  $r_g$  at the input appears as an additional term  $r_g/R_s$  in the expressions for  $F$ . Practically,  $r_g$  and  $r_b$  are very important in determining the NF, as well as input impedance of the LNA. They determine the minimum noise-factor ( $F_{\min}$ ) of a transistor [29].

Using these simplifying assumption, the equivalent input current and voltage sources for the amplifier in Fig. 5 are

$$\begin{cases} i_n = \alpha_{nd} \cdot i_{nd} + \alpha_{ng} \cdot i_{ng} \\ c_n = Z_{nd} \cdot i_{nd} + Z_{ng} \cdot i_{ng} \end{cases} \quad (7)$$

where

$$\begin{aligned} \alpha_{ng} &= \frac{Z_{gs}(1 - g_m Z_{gd})}{Z_{gs} + Z'_s(1 + g_m Z_{gs}) - g_m Z_{gs} Z_{gd}} \\ \alpha_{nd} &= -\frac{Z_{gs} + Z_{gd}}{Z_{gs} + Z'_s(1 + g_m Z_{gs}) - g_m Z_{gs} Z_{gd}} \\ Z_{ng} &= -\frac{g_m Z_{gs} Z'_s Z_{gd}}{Z_{gs} + Z'_s(1 + g_m Z_{gs}) - g_m Z_{gs} Z_{gd}} \\ Z_{nd} &= -\frac{Z_{gd}(Z_{gs} + Z'_s)}{Z_{gs} + Z'_s(1 + g_m Z_{gs}) - g_m Z_{gs} Z_{gd}} \end{aligned} \quad (8)$$

combining (6) and (7) results in the following expression for the noise factor  $F$ :

$$\begin{aligned} F &= 1 + |\alpha_{nd} + Y_s Z_{nd}|^2 \cdot \frac{\overline{i_{nd}^2}}{\overline{i_s^2}} + |\alpha_{ng} + Y_s Z_{ng}|^2 \cdot \frac{\overline{i_{ng}^2}}{\overline{i_s^2}} \\ &\quad + \frac{2 \operatorname{Re} \{ (\alpha_{nd} + Y_s Z_{nd})(\alpha_{ng} + Y_s Z_{ng})^* \cdot \overline{i_{nd} i_{ng}^*} \}}{\overline{i_s^2}} \end{aligned} \quad (9)$$

where the second term is due to drain current noise, the third term is caused by gate-induced current noise, and the last term is the result of the correlation between the two noise sources (a similar correlation term exists between the collector and base shot noise of a bipolar transistor [50]).

Note that (9) is quite general and can be used for the design of broad-band, narrow-band, or concurrent multiband LNAs using any kind of transistor, as long as the small-signal noise model of the transistor is known. We will use this expression to compare the effect of various noise sources in different topologies.

In the case of a MOS transistor, noise current densities are known to be [50]

$$\begin{aligned} \overline{i_{nd}^2} &= 4kT\gamma g_{d0} \Delta f \\ \overline{i_{ng}^2} &= 4kT\delta g_g \Delta f \\ g_g &= \frac{\omega^2 C_{gs}^2}{5g_{d0}} \\ \overline{i_{nd} i_{ng}^*} &= c^* \cdot \sqrt{\overline{i_{nd}^2}} \sqrt{\overline{i_{ng}^2}} \end{aligned} \quad (10)$$

where  $c^*$  is the complex conjugate of the correlation coefficient between gate and drain noise currents.

We can simplify (8) if we ignore  $Z_{gd}$  (setting  $Z_{gd} = \infty$ ), assuming it is dominated by the small gate-drain capacitor  $C_{gd}$  (i.e., a high impedance compared to other impedances in the circuit at the frequency of interest). Also, we can use the noise transformation of (24) to include the effect of an arbitrary gate series impedance  $Z_g$ . Under these assumptions, the coefficients in (7) will become

$$\begin{aligned} \alpha_{nd} &= \frac{1}{g_m Z_{gs}} \\ \alpha_{ng} &= 1 \\ Z_{nd} &= \frac{Z_g + Z_{gs} + Z_s}{g_m Z_{gs}} \\ Z_{ng} &= Z_g + Z_s \end{aligned} \quad (11)$$

which can be used in (9) to estimate the NF of the LNA.

To gain more design insight, for the time being let us focus on the effect of the drain current noise, which is often the most dominant noise source in the amplifier. In this case, the noise factor is given by

$$F = 1 + |1 + Y_s(Z_g + Z_{gs} + Z'_s)|^2 \cdot \frac{1}{g_m^2 |Z_{gs}|^2} \cdot \frac{\overline{i_{nd}^2}}{\overline{i_s^2}}. \quad (12)$$

Since  $Z_g$ ,  $Z_{gs}$ , and  $Z'_s$  are assumed to be passive networks, and  $Y_s$  is a real admittance in all the practical cases (e.g.,  $1/50 \Omega$ ), the minimum value of the first term of the product above occurs when

$$Z_g + Z_{gs} + Z'_s = 0 \quad \forall \omega_i \quad (13)$$

for all frequency bands,  $\omega_i$ . For this to be possible, all three passive networks should be lossless. Therefore, in practice, one should choose the passive networks  $Z_g$ ,  $Z_{gs}$ , and  $Z'_s$  to minimize  $Z_g + Z_{gs} + Z'_s$  at each center frequency of interest,  $\omega_i$ . We will refer to this minimum real value at each center frequency as  $R_{\min}(\omega_i)$ . This is the same constraint that we referred to in the previous subsection on the input matching of concurrent LNAs.

The above-mentioned general constraint for a concurrent multiband LNA should also work in the more straightforward case of a single-band LNA. In this case, if  $Z_{gs}$  is simply the

gate-source capacitance, and if  $Z_g$  and  $Z'_s$  networks consist of single inductors, we can satisfy (13) by setting

$$(L_s + L_g)C_{gs}\omega_0^2 = 1 \quad (14)$$

where  $\omega_0$  is the center frequency of interest in the single-band LNA. This is the same design equation used in [23].

In addition to the minimization of  $Z_g + Z_{gs} + Z'_s$  at each center frequency of interest, (12) suggests that using higher  $Z_{gs}$  and higher device  $g_m$  can lower the NF further. One simple way of obtaining a large  $Z_{gs}$  is to keep the  $Z_{gs}$  network as simple as the intrinsic gate-source capacitance  $C_{gs}$ , i.e., using no explicit component between the gate and the source.

Different transistor technologies result in different noise performances. To compare different technologies, we can rewrite the NF expression of (12) as the following general expression valid for both MOS and bipolar transistors:

$$F = 1 + 2k_L \frac{IR_s}{V_{\text{char}}} \left( \frac{\omega}{\omega_T} \right)^2$$

$$k_L = \left( 1 + \frac{R_{\min}(\omega)}{R_s} \right)^2 \quad (15)$$

where  $\omega_T$  is the small-signal unity frequency of the transistor<sup>6</sup> and  $I$  is the drain (or collector) current. The characteristic voltage,  $V_{\text{char}}$ , is defined as  $V_{\text{char}} = 4kT/q$  for a bipolar transistor, and  $V_{\text{char}} = (V_{\text{gs}} - V_T)/\gamma$  and  $V_{\text{char}} = E_C L/\gamma$  for a long-channel and short-channel velocity-saturated MOS transistor, respectively.

Keeping in mind that to arrive at (15) we ignored the effect of the gate-induced current noise (or base shot noise), as well as the gate (base) series resistance noise, we can use (15) to make an approximate comparison between the noise performance of bipolar and MOS transistors. It can be seen from (15) that NF decreases with increasing  $V_{\text{char}}$ , assuming constant  $\omega_T$ . Table I shows the values of  $V_{\text{char}}$  and  $\omega_T$  for a bipolar junction transistor as well as a few typical short-channel MOS transistors.<sup>7</sup> It is also noteworthy that, under these assumptions, a CMOS LNA will have a smaller NF compared to its bipolar counterpart because of its higher  $V_{\text{char}}$ .<sup>8</sup> Nevertheless, this simplistic analysis is not completely adequate and, hence, a more accurate comparison will be performed next.

Taking the effect of the input resistance, gate-induced noise or base-shot noise into account, the following expression can be derived for the NF:

$$F_{\text{Bipolar}} = 1 + \frac{r_b}{R_s} + 2k_L \frac{I_C R_s}{V_{\text{char}}} \left( \frac{\omega}{\omega_T} \right)^2$$

<sup>6</sup>Note that  $\omega_T$  is a fixed value for a given deep short-channel MOS transistor biased in velocity saturation region, but it depends on current and device width in a long-channel MOS transistor.  $\omega_T$  is current-dependent in bipolar transistor, but the dependency is smaller for large collector currents and smaller junction capacitors.

<sup>7</sup>The  $E_C$  values in Table I are derived from curves of  $g_m - V_{\text{gs}}$  and  $g_{d0} - V_{\text{gs}}$  obtained from simulation using BSIM3v3 models and assuming  $g_{d0}/g_m = 2(V_{\text{gs}} - V_{th})/E_C L$  (i.e., deep velocity saturated device). Also we assume a  $\gamma$  of 2 and use (4) to obtain  $\omega_T$  of MOS transistors.

<sup>8</sup>It should be noted that the same  $V_{\text{char}}$  appears in the phase-noise expressions of ring oscillators resulting in a similar argument suggesting that ring oscillators in current CMOS technologies offer lower phase noise than their bipolar counterparts [53].

TABLE I

COMPARISON OF  $V_{\text{char}}$ , AND  $\omega_T$  IN DIFFERENT SUBMICROMETER CMOS PROCESSES

| Process technology                                                   | $E_C$ (V/m)        | $V_{\text{char}}$ (V) | $\omega_T$ (rad/s)                     |

|----------------------------------------------------------------------|--------------------|-----------------------|----------------------------------------|

| Silicon Bipolar<br>( $\tau_p = 3.67$ ps)                             | N/A                | 0.140                 | $2\pi \times 37\text{-GHz}$<br>@ 10 mA |

| 0.35- $\mu\text{m}$ CMOS<br>( $L_{\text{eff}} = 0.27\ \mu\text{m}$ ) | $5.46 \times 10^6$ | 0.74                  | $2\pi \times 42\text{-GHz}$            |

| 0.25- $\mu\text{m}$ CMOS<br>( $L_{\text{eff}} = 0.21\ \mu\text{m}$ ) | $4.27 \times 10^6$ | 0.45                  | $2\pi \times 59\text{-GHz}$            |

| 0.18- $\mu\text{m}$ CMOS<br>( $L_{\text{eff}} = 0.16\ \mu\text{m}$ ) | $3.02 \times 10^6$ | 0.24                  | $2\pi \times 63\text{-GHz}$            |

| 0.15- $\mu\text{m}$ CMOS<br>( $L_{\text{eff}} = 0.13\ \mu\text{m}$ ) | $3.57 \times 10^6$ | 0.26                  | $2\pi \times 102\text{-GHz}$           |

$$+ \left( k_L + \frac{1}{\left( 4 \left( \frac{\omega}{\omega_T} \right) \cdot \frac{I_C R_s}{V_{\text{char}}} \right)^2} \right)$$

$$\cdot 2 \frac{I_C R_s}{V_{\text{char}}(\beta + 1)} \quad (16a)$$

$$F_{\text{CMOS}} = 1 + \frac{r_g}{R_s} + k_L \left( \frac{\omega C_{gs}}{g_m} \right)^2 \cdot \gamma g_{d0} R_s$$

$$+ \left( k_L + \left( \frac{1}{\omega C_{gs} R_s} \right)^2 \right) \cdot \delta \frac{\omega^2 C_{gs}^2}{5g_{d0}} R_s$$

$$+ 2\sqrt{k_L} \frac{(\omega C_{gs})^2}{g_m} \cdot |c| \cdot \sqrt{\frac{\gamma \delta}{5}} \cdot R_s. \quad (16b)$$

Note that no assumptions about the single-band operation of the amplifier were made and, hence, these equations are valid in the general case of a concurrent multiband LNA.

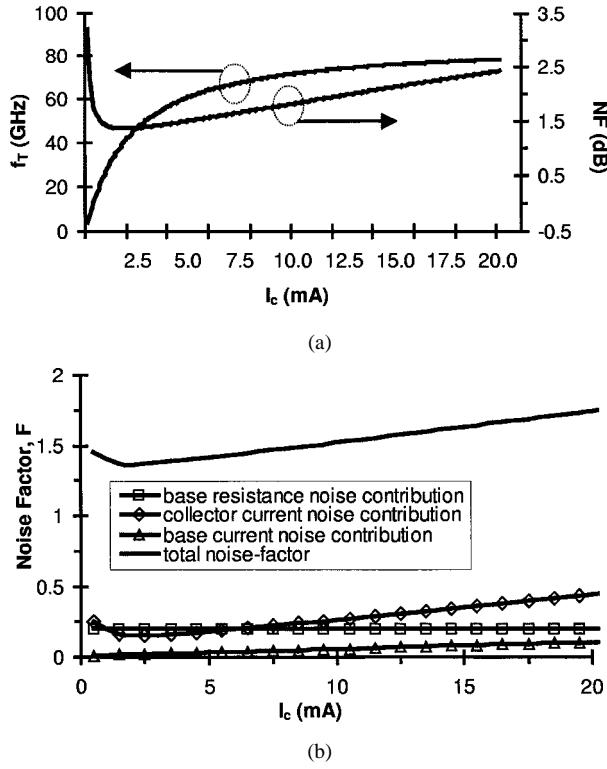

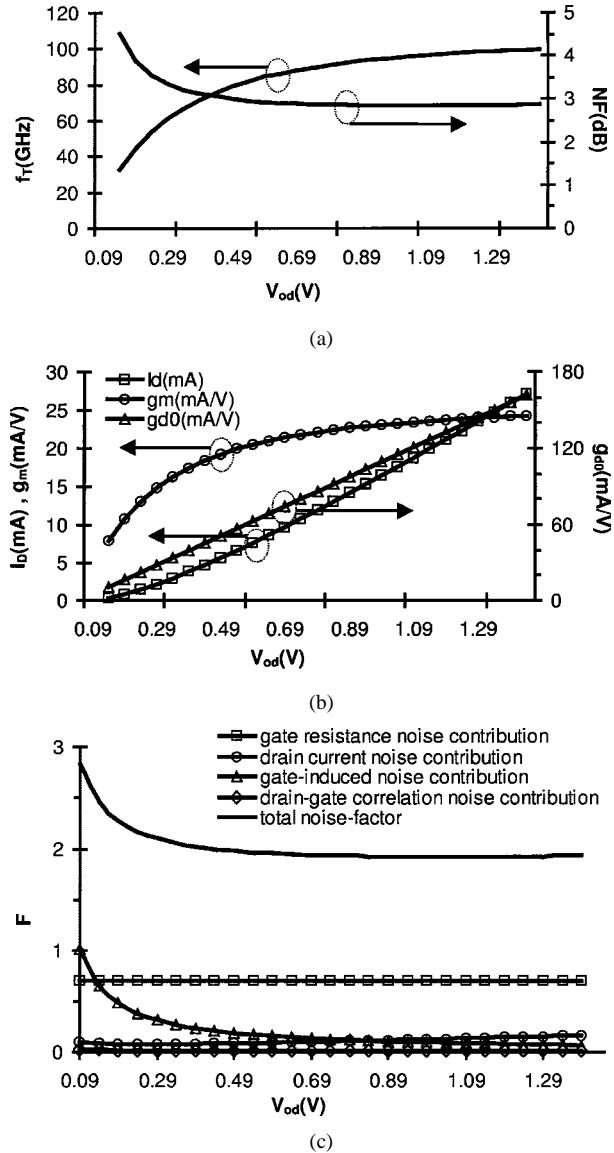

Fig. 7(a) shows plots of the NF and  $\omega_T$  versus collector current for a bipolar transistor using (16a). The contributions of different noise sources to the overall noise factor,  $F$ , are shown in Fig. 7(b).

Now we can make a few observations in this common emitter configuration. First, at low frequencies compared to  $\omega_T$ , NF is dominated by the base shot noise, while at higher frequencies the collector shot noise is the primary noise contributor. Second, for large collector currents, collector shot noise dominates the NF and, therefore, increasing the collector current *deteriorates* the noise factor  $F$  in a linear fashion. For smaller collector currents, the effect of base shot noise on the NF increases and the total NF degrades again. Third, a reduction in the collector current will lower the cutoff frequency<sup>9</sup>  $\omega_T$  and, hence, increases the NF. As can be seen, this is similar to the well-known behavior of a single bipolar transistor amplifier where the  $F_{\min}$  reaches a minimum for a certain collector current [29].

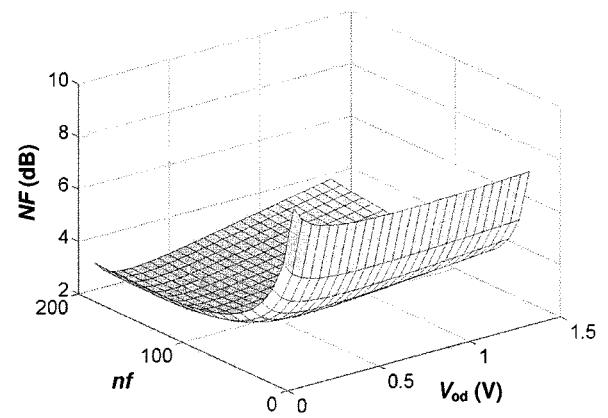

In the case of MOS transistors, there are more degrees of freedom in the design, such as finger width  $W_f$  and the number of fingers  $n_f$ . It is clear that the fingers should be as short as the technology allows minimizing  $r_g$  for any given overall device width,  $W$ . Of course, we can control  $W$  by adjusting  $n_f$  ( $W = W_f \cdot n_f$ ). A larger  $W$  results in a smaller  $r_g$  and, hence, a smaller gate-resistance noise contribution. However,

<sup>9</sup>More accurately,  $\omega_T$  is given by  $\omega_T^{-1} = \tau_T = \tau_F + C_{je}/g_m + C_{\mu}/g_m$

Fig. 7. (a) NF and  $f_T$  for a bipolar transistor with  $\tau_F = 3.67$  ps. (b) Different noise contributions to the total NF from (16a) (NF numbers for 5.8 GHz).

while a larger  $W$  increases the transistor's transconductance  $g_m$ , it also increases the drain current consumption and has a negative overall effect on drain noise current contribution to the amplifier's NF. Therefore, there is an optimum  $W$  and, hence, an optimum  $n_f$  resulting in the lowest NF in this topology (Fig. 8). This approach does not compromise the voltage gain significantly, as it is shown in the next section that the voltage gain of this amplifier is independent of device transconductance and the number of fingers to the first order.

The other parameter of interest is the gate-source overdrive voltage  $V_{od} = V_{gs} - V_{th}$  of the MOS transistor. For small values of  $V_{od}$ ,  $g_{d0}$  and  $g_m$  increase linearly with  $V_{od}$  until velocity saturation occurs and then  $g_m$  becomes constant. Meanwhile,  $g_{d0}$  and consequently the device noise keep increasing with  $V_{od}$ . As can be seen from (16a) and (16b), the drain noise contribution to  $F$  is proportional to  $g_{d0}$  and inversely proportional to the square of  $g_m$ . Therefore, NF drops with  $V_{od}$  in the beginning and then rolls back up, as can be seen in Fig. 9(a). It also shows graphs of  $I_d$ ,  $g_m$  and  $g_{d0}$  versus  $V_{od}$  for the same transistor in a typical 0.18- $\mu$ m CMOS process. As can be seen from the figure, further increase of  $V_{od}$  beyond the optimum NF point will degrade the noise factor and increase the power dissipation. The individual contributions of different noise sources of the same transistor to the total NF are shown in Fig. 9(c).

In practice, passives and substrate resistance noise add to the NF, especially in high-frequency circuits where their relative contributions can be substantial [55]. Also, it is noteworthy that the noise of the equivalent channel resistance  $r_{gs}^{10}$  in series with  $C_{gs}$  at high frequencies is already taken into account in the gate-

Fig. 8. NF of a 0.18- $\mu$ m CMOS transistor at 5.8 GHz with finger width of 2  $\mu$ m versus  $n_f$  and  $V_{od}$ .

Fig. 9. (a) NF,  $f_T$  of a  $20 \times 2.5 \mu/0.18 \mu$  CMOS transistor. (b)  $I_d$ ,  $g_m$ ,  $g_{d0}$  of the transistor. (c) Different noise contributions to the total NF from (16b) (NF numbers at 5.8 GHz).

induced noise expressions in (10). Some authors (e.g., [56]) consider the channel resistance noiseless while others (e.g., [25])

<sup>10</sup>It should be noted that this channel resistance is different from  $r_{on}$  of MOS transistor in the linear (ohmic) region.

modeled it as a noisy resistor. However, it should be noted that channel resistance and gate-induced noise originate from the same distributed gate effect (or nonquasi-static effect) in MOS transistors and the complete noise expressions similar to (10) should be used [50]. Although its noise is already taken into account, channel resistance  $r_{gs}$  will affect the expressions for input matching and should be considered in the design process [57], [56].

Once again, we would like to remind the reader that the above discussion is equally valid for concurrent multiband LNAs, as well as single-band implementations, as no explicit assumptions regarding the number of frequency bands have been made.

#### D. Load Circuit, Output Matching, and Gain

While the input and output of a stand-alone LNA usually need to be matched to  $50 \Omega$  to transfer the power efficiently using transmission lines, the output of an LNA in an integrated front-end does not necessarily have to be matched in a similar way. Usually an integrated LNA drives the capacitive input of the first down-conversion mixer in the receiver chain and, hence, it is not desirable to match the output to a real impedance. This difference also explains why it is more common to report some form of power gain (e.g.,  $G_p$  or  $S_{21}$ ) for stand-alone LNAs, and the voltage gain  $A_v$  for the LNAs in integrated front-end circuits. The NF expression for the receiver using voltage gain and input-referred voltage sources can be derived when the output of the LNA is not impedance matched [18].

Assuming no body effect ( $g_{mb} = 0$ ) and a small  $C_{gd}$  ( $Z_{gd} = \infty$ ), the voltage gain expression of (22) simplifies to

$$|A_v| = \left| \frac{V_{\text{out}}}{V_{\text{in}}} \right| = \left| \frac{g_m Z_{gs} Z'_L}{Z_{\text{in}}} \right| \quad (17)$$

which can be used to calculate the gain at all frequencies. At the frequency bands of interest where (13) holds for minimum NF, (22) further reduces to

$$|A_v| = \left| \frac{Z'_L}{Z'_s + \frac{R_{\text{min}}}{g_m Z_{gs}}} \right| \approx \left| \frac{Z'_L}{Z_s} \right|. \quad (18)$$

If  $Z_s$  is implemented as an inductor to provide the real part of the input impedance, its value is given by (2) which is almost independent of the bias current in a deep velocity-saturated short-channel MOS transistor and also in a bipolar transistor as mentioned in Section IV-B. Therefore, voltage gain given by (18) will be independent of current to the first order. In this case, increasing the bias current will only increase the NF with no significant improvement in  $A_v$ .

To achieve the highest gain and selectivity at the frequencies of interest, it is desirable to use a multiresonant load at the output whose impedance is maximum at the frequencies of interest. An example of such load networks will be shown in Section V.

#### E. Concurrent Multiband LNA Linearity Measures

Linearity is an important measure in the receiver as it determines the size of the largest signal that can be handled by

Fig. 10. Illustration of cross-band intermodulation.

the receiver and controls its dynamic range. The linearity of a single-band LNA is often described using its  $n$ th-order intercept point  $IP_n$  and 1-dB compression point  $CP1$ . In a concurrent multiband LNA, the  $IP_3$  and  $CP1$  in each band with no significant signal in the other bands are still important and will be referred to as  $IP_{3\text{inband}}$  and  $CP1_{\text{inband}}$ , respectively. However, due to its concurrent multiband nature, other nonlinearity measures should also be considered. A strong signal in any band can compress the LNA gain at all frequencies. A *cross-band* compression measure can be defined as the signal power in band  $A$  that causes a 1-dB drop in the small-signal gain in band  $B$  which will be denoted as  $CP1_{A>B}$ . In addition to this cross-band compression, in-band signals from different desired bands can mix due to the amplifier's nonlinearity and cause in-band undesired signals, as shown in Fig. 10. We show the input intercept point associated with this cross-band intermodulation as  $IP_{n\text{crossband}}$ , where  $n$  is the order of nonlinearity leading to this effect.

We can derive expressions for the nonlinearity measures of concurrent multiband LNAs in terms of device nonlinearity similar to the case of single-band LNAs [60]. We can also relate these cross-band nonlinearity measures to the single-band ones.

Assuming the amplifier output has a third-order polynomial dependence on the input

$$V_{\text{out}} = a_1 V_{\text{in}} + a_2 V_{\text{in}}^2 + a_3 V_{\text{in}}^3 \quad (19)$$

we can calculate the in-band and cross-band 1-dB compression points

$$CP1_{\text{inband}} = \sqrt{\frac{4}{3} (10^{-0.1} - 1) \cdot \frac{a_1}{a_3}} \quad (20a)$$

$$CP1_{\text{crossband}} = \sqrt{\frac{2}{3} (10^{-0.1} - 1) \cdot \frac{a_1}{a_3}}. \quad (20b)$$

As can be seen from the above equations, the cross-band 1-dB compression occurs 3 dB earlier than the in-band one. This suggests that, for the same amount of nonlinearity, a concurrent multiband LNA needs to be 3 dB more linear than its single-band counterpart. If different applications at various bands have maximum signal powers, the concurrent multiband LNA has to be 3 dB more linear for the strongest signal when compared to a single-band LNA.

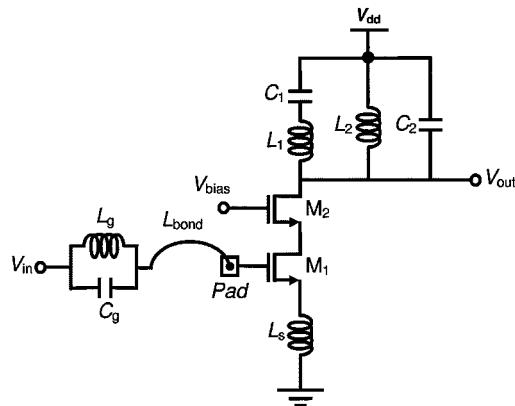

Fig. 11. Concurrent dual-band CMOS LNA (biasing circuitry not shown).

## V. LNA DESIGN EXAMPLES AND MEASUREMENT RESULTS

Having established the theoretical framework for the design of concurrent multiband LNAs, in this section we demonstrate an example of a dual-band concurrent LNA operating at 2.45 and 5.25 GHz. It should be noted that this example shows just one of the many possible implementations following the general treatment of the previous section.

While (21) and (23) provide numerous ways to design the input matching network for any number of frequency bands, we can use the more simplified expressions in (1) and (13) to achieve simultaneous input matching and minimum NF at two frequencies. We note that (2) can also be satisfied for multiple frequencies if  $Z_{gs}$  and  $Z_s$  are dual circuits, i.e.,  $Z_{gs}Z_s = k$ , where  $k = R_{in}/g_m$  is constant. As mentioned earlier, we need to maximize  $Z_{gs}$  in order to minimize the NF. One way to obtain a reasonably large  $Z_{gs}$  is to use a transistor with minimum channel length and no extra passive elements between the gate and the source. The condition set by (2) can be satisfied using a single on-chip source degeneration inductor similar to the single-band case of [23] and [24]. Since passive components realized on silicon substrate are normally very lossy, having them at the input of the amplifier seriously degrades the NF of the LNA. To fulfill (13) at both frequencies, a parallel  $LC$  network in series with the inevitable inductance of the bonding wire and package lead is used as shown in Fig. 11. The parallel  $LC$  network of  $Z_g$  is designed to resonate with  $Z_{gs} + Z_s$  at both frequency bands of interest.

The drain load network should exhibit high impedance only at frequencies of interest in order to achieve concurrent multi-band gain. This requirement can be fulfilled by adding a series *LC* branch in parallel with the parallel *LC* tank of a single-band LNA, as shown in Fig. 11. Each series *LC* branch introduces a zero in the gain transfer function of the LNA at its series resonant frequency that determines the frequency of the notches in the transfer function. This notch is used to enhance the image rejection of the receiver, as discussed in Section III and shown in Fig. 4. Equation (16b) was used to obtain the optimum device size and the dc current.

A concurrent dual-band CMOS LNA implemented in a 0.35- $\mu$ m BiCMOS technology using only CMOS transistors operates at 2.45 and 5.25 GHz. The input parallel resonator

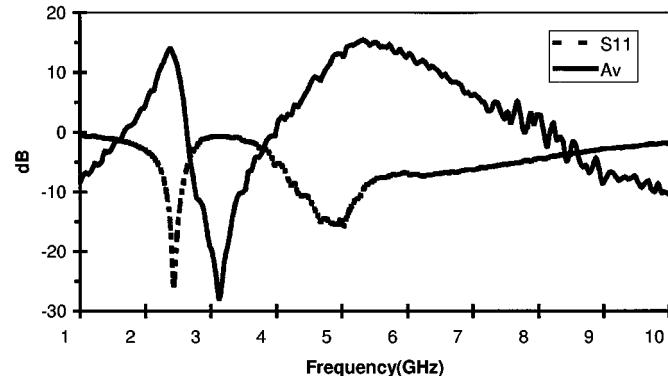

Fig. 12. Measured voltage gain and  $S_{11}$  in concurrent dual-band CMOS LNA of Fig. 11.

TABLE II

PERFORMANCE SUMMARY OF THE CONCURRENT DUAL-BAND CMOS LNA

| Frequency                       | 2.45 GHz                       | 5.25 GHz                   |

|---------------------------------|--------------------------------|----------------------------|

| Voltage Gain                    | 14 dB                          | 15.5 dB                    |

| $S_{11}$                        | -25 dB                         | -15 dB                     |

| NF                              | 2.3 dB                         | 4.5 dB                     |

| Input IP3 <sub>in-band</sub>    | 0.0 dBm                        | 5.6 dBm                    |

| Input CP1 <sub>in-band</sub>    | -8.5 dBm                       | -1.5 dBm                   |

| Input CP1 <sub>A&gt;B</sub>     | $CP1_{2.4>5.2} = -11.5$ dBm    | $CP1_{5.2>2.4} = -5.7$ dBm |

| Input IP4 <sub>cross-band</sub> | 7.5 dBm                        |                            |

| DC Current                      | 4 mA                           |                            |

| Supply Voltage                  | 2.5 V                          |                            |

| Active Device                   | 0.35- $\mu$ m CMOS transistors |                            |

Fig. 13. Chip micrograph for the concurrent dual-band CMOS LNA in Fig. 11.

is made using a 0.9-pF porcelain multilayer capacitor and a 2.7-nH chip inductor.

Fig. 12 shows the measured voltage gain  $A_v$  and input reflection coefficient  $S_{11}$  of the amplifier up to 10 GHz. The LNA achieves narrow-band voltage gains of 14 and 15.5 dB, input return losses of 25 and 15 dB, and NFs of 2.3 and 4.5 dB at

TABLE III

COMPARISON OF EXISTING SINGLE-BAND CMOS LNAs AND THE CONCURRENT MULTI-BAND LNA AT THE SAME FREQUENCY BANDS (S-BAND AND C-BAND)

| Ref.             | Tech.               | Freq.    | NF(dB) | Gain (dB)              | $S_{11}$ (dB) | $IP_3$ (dBm)   | $CP_{1dB}$ (dBm) | Power             |

|------------------|---------------------|----------|--------|------------------------|---------------|----------------|------------------|-------------------|

| [62]             | 0.25- $\mu$ m PHEMT | 5.4GHz   | 0.76   | 16                     | -15           | N/A            | N/A              | N/A               |

| [64]             | 0.4- $\mu$ m GaAs   | 5.2 GHz  | 1.7    | 14.5                   | N/A           | -10<br>(Input) | N/A              | 3 mA<br>(3 V)     |

| [63]             | GaAs HBT            | 5.7 GHz  | 2.9    | 16.2                   | -7            | 7<br>(Output)  | 21<br>(Output)   | 21 mA<br>(3.5 V)  |

| [65]             | SiGe HBT            | 5.8 GHz  | 1.6    | 17                     | N/A           | N/A            | N/A              | 7.5 mA<br>(4.5 V) |

| [66]             | 0.6- $\mu$ m CMOS   | 2.4 GHz  | 2.3    | 17.5 (A <sub>v</sub> ) | -19           | 1.8<br>(Input) | -9<br>(Input)    | 8 mA<br>(3.3 V)   |

| [59]             | 0.24- $\mu$ m CMOS  | 5 GHz    | 4.8    | 18 (A <sub>v</sub> )   | -12           | N/A            | N/A              | 3.6 mA<br>(2 V)   |

| [67]             | 0.25- $\mu$ m CMOS  | 5 GHz    | 2.5    | 16 (G <sub>p</sub> )   | -9.5          | N/A            | N/A              | 16 mA<br>(3 V)    |

| This Work<br>[7] | 0.35- $\mu$ m CMOS  | 2.45 GHz | 2.3    | 14 (A <sub>v</sub> )   | -25           | 0<br>(Input)   | -8.5<br>(Input)  | 4 mA<br>(2.5 V)   |

|                  |                     | 5.25 GHz | 4.5    | 15.5 (A <sub>v</sub> ) | -15           | 5.6<br>(Input) | -1.5<br>(Input)  |                   |

2.45 and 5.25 GHz, respectively. In the course of the NF measurements, special attention was paid to *avoid* methods outlined in [58]. It drains 4 mA of current from a 2.5-V supply voltage. The notch due to the LNA is about 40 dB deeper than the peaks, which directly translates to the same amount of improvement in image rejection. Due to the large difference between the notch and pass-band frequencies, no elaborate tracking loops such as those proposed in [59] are necessary to obtain extra image rejection. The single-ended nature of the LNA makes external Baluns unnecessary. Measurements of six different chips with three different boards and off-chip components show good repeatability without using the sliding capacitor input matching adjustment commonly used in a single-band case [61].

This concurrent dual-band LNA demonstrates input-referred in-band  $IP_3$ s of 0 and 5.6 dBm, and in-band  $CP_1$ s of -8.5 and -1.5 dBm at 2.45- and 5.25-GHz bands, respectively. For this particular frequencies, two tones at 2.50 and 5.15 GHz can combine through the fourth-order nonlinearity to produce an in-band signal at 2.35 GHz (i.e.,  $4 \times 2.50 - 1 \times 5.15 = 2.35$ ). The measurements show that this input referred to as  $IP_{4\text{crossband}}$  is 7.5 dBm. The LNA exhibits a  $CP_{1,2.4>5.2}$  of -11.5 dBm and a  $CP_{1,5.2>2.4}$  of -5.7 dBm. Note the 3-dB difference in in-band and cross-band compression points, as predicted by (20a) and (20b).

Table II summarizes the measured performance of the fabricated concurrent dual-band LNA depicted in Fig. 13. The chip occupies an area of 0.8 mm  $\times$  0.8 mm including pads and ESDs.

Table III compares the performance of this concurrent dual-band LNA with previously published single-band LNAs working in one of the same frequency bands. The NF,  $S_{11}$ , and power dissipation are comparable or better than previously published nonconcurrent single-band CMOS LNAs.

## VI. CONCLUSION

The new concept of a concurrent multiband LNA with the intention of use as the essential part of a concurrent multiband receiver is introduced. One implementation of such a new concurrent dual-band receiver architecture capable of simultaneous

Fig. 14. Simplified small-signal model of Fig. 5 when bulk is ac grounded.

operation at two different frequency bands is introduced. It uses a novel concurrent dual-band LNA, combined with an elaborate frequency conversion scheme to reject the out-of-band signals. A general methodology is also provided to achieve simultaneous narrow-band gain and input matching while offering a low NF in concurrent multiband LNAs. The effectiveness of the proposed methodology is demonstrated through measurement results of a CMOS implementation of the integrated concurrent dual-band LNA that achieves a superior NF,  $S_{11}$ , and power dissipation over previously published nonconcurrent and/or single-band LNAs.

## APPENDIX A

Fig. 14 is the equivalent small-signal model for the circuit in Fig. 5 where the bulk is ac-grounded. To simplify this equivalent model, we define  $Z'_s = Z_s || Z_{sb}$  and  $Z'_L = Z_L || Z_{db}$ , where  $Z_{sb}$ ,  $Z_{db}$  are the source-bulk and drain-bulk impedances.

The transistor's output resistor,  $r_o$ , can be neglected, because it is relatively large compared to relatively small impedances in an RF circuit. Then, the small-signal input impedance and the voltage gain of this circuit are given by

$$Z_{in} = Z_g + (Z'_L + Z_{gd}) \cdot \frac{Z_{gs} + Z'_s(1 + g_m Z_{gs})}{Z_{gs} + [Z'_s(1 + g_m Z'_L) + Z'_L] \cdot (1 + g_m Z_{gs}) + Z_{gd}} \quad (21)$$

Fig. 15. Effect of adding an impedance to the input of a two-port network on equivalent input noise sources: (a) series impedance and (b) parallel impedance.

$$A_V = \frac{Z_{in} - Z_g}{Z_{in}} \cdot (Z'_L \parallel Z_{gd}) \cdot \left[ \frac{1}{Z_{gd}} - \frac{g_m Z_{gs} - g_{mb} Z'_s}{Z_{gs} + Z'_s [1 + (g_m + g_{mb}) Z_{gs}]} \right]. \quad (22)$$

The input admittance can also be written as the parallel combination of equivalent admittances, i.e.,

$$Y_{in} = \frac{1}{Z_g} \cdot \left\{ \frac{1}{Z_{gs} + Z'_s (1 + g_m Z_{gs})} + \frac{1}{Z'_L + Z_{gd}} + \frac{g_{mb}}{1 + \frac{Z_{gd}}{Z'_L}} \right\} + \frac{1}{1 + \frac{Z_{gd}}{Z'_L}} \cdot (g_m - g_{mb}) \cdot \frac{Z_{gs}}{Z_{gs} + Z'_s (1 + g_m Z_{gs})} \quad (23)$$

## APPENDIX B

Adding a noiseless<sup>11</sup> one-port network with an impedance  $Z_1$  in series with the input of a given noisy two-port network [see Fig. 15(a)] modifies its input referred equivalent current and voltage sources in the following way:

$$\begin{aligned} i'_n &= i_n \\ e'_n &= e_n + Z_1 \cdot i_n. \end{aligned} \quad (24)$$

Similarly, adding a noiseless one-port network with an admittance  $Y_1$  in parallel with the input of a given noisy two-port network [see Fig. 15(b)] modifies its input referred equivalent current and voltage sources as follows:

$$\begin{aligned} i'_n &= i_n + Y_2 \cdot e_n \\ e'_n &= e_n. \end{aligned} \quad (25)$$

## ACKNOWLEDGMENT

The authors would like to thank members of the Caltech High-Speed Integrated Circuits (C.H.I.C.) and Microwave and

<sup>11</sup>In the case of a noisy  $Z_1$ , its equivalent voltage noise source will be simply added to  $e_n$ .

RF groups, particularly, I. Aoki, H. Wu, L. Chung, and S. Kee for assistance with measurements, and A. Komijani, D. Lu, B. Analui, and M. Morgan for their comments on the manuscript. The authors also thank Conexant Systems, Newport Beach, CA, for chip fabrication, especially R. Magoon, F. Intveld, R. Hlavac, A. Vo, J. Powel, T. Whistler, and S. Lloyd for their support during chip tape-out. The authors also appreciate helpful technical discussions with S. Weinreb, Jet Propulsion Laboratory, Pasadena, CA, H. Samavati, Stanford University, Stanford, CA, and Y. Cheng, Conexant Systems, Newport Beach, CA.

## REFERENCES

- [1] E. Armstrong, "A new system of short wave amplification," *Proc. IRE*, vol. 9, pp. 3–11, Feb. 1921.

- [2] S. Wu and B. Razavi, "A 900-MHz/1.8-GHz CMOS receiver for dual-band applications," *IEEE J. Solid-State Circuits*, vol. 33, pp. 2178–2185, Dec. 1998.

- [3] J. Tham, M. Margrait, B. Pregardier, C. Hull, R. Magoon, and F. Carr, "A 2.7V 900-MHz dual-band transceiver IC for digital wireless communication," *IEEE J. Solid-State Circuits*, vol. 34, pp. 286–291, Mar. 1999.

- [4] J. Imbornone, J. Mourant, and T. Tewksbury, "Fully differential dual-band image reject receiver in SiGe BiCMOS," in *IEEE RFIC Symp. Dig.*, 2000, pp. 147–150.

- [5] W. Titus, R. Croughwell, C. Schiller, and L. DeVito, "A Si BJT dual-band receiver IC for DAB," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.*, vol. 1, New York, NY, 1998, pp. 345–348.

- [6] R. J. Hasler, "Adding GPS to CDMA mobile-telephone handsets," *Microwave RF*, pp. 69–78, Mar. 2001.

- [7] H. Hashemi and A. Hajimiri, "Concurrent dual-band CMOS low noise amplifiers and receiver architectures," in *VLSI Circuits Symp. Dig.*, June 2001, pp. 247–250.

- [8] H. T. Friis, "Noise figure of radio receivers," *Proc. IRE*, pp. 419–422, July 1944.

- [9] R. Engelbrecht and K. Kurokawa, "A wide-band low-noise L-band balanced transistor amplifier," *Proc. IEEE*, vol. 53, pp. 237–247, Mar. 1965.

- [10] C. Leitch, "Microwave field-effect transistors," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-24, pp. 279–300, June 1976.

- [11] Y. Mimino, M. Hirata, K. Nakamura, K. Sakamoto, Y. Aoki, and S. Kuroda, "High gain-density  $K$ -band P-HEMT LNA MMIC for LMDS and satellite communication," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 2000, pp. 17–20.

- [12] P. Marsh, S. Chu, S. Lardizabel, R. Leoni, S. Kang, R. Wohlert, A. Bowley, W. Hoke, R. McTaggart, P. Lemonias, P. McIntosh, and T. Kazior, "Low noise metamorphic HEMT devices and amplifiers on GaAs substrates," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.*, vol. 1, 1999, pp. 105–108.

- [13] H. Dodo, Y. Amamiya, T. Niwa, M. Mamada, S. Tanaka, and H. Shimawaki, "Microwave low-noise GaAs HBTs," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.*, vol. 2, 1998, pp. 693–696.

- [14] D. Greenberg, D. Ahlgren, G. Freeman, S. Subbanna, V. Radisic, D. Harvey, C. Webster, and L. Larson, "HBT low-noise performance in a  $0.18\mu\text{m}$  SiGe BICMOS technology," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.*, vol. 1, 2000, pp. 9–12.

- [15] F. Reif, *Fundamentals of Statistical and Thermal Physics*. New York: McGraw-Hill, 1985.

- [16] D. Ham and A. Hajimiri, "Concepts and methods in optimization of integrated LC VCOs," *IEEE J. Solid-State Circuits*, vol. 36, pp. 896–909, June 2001.

- [17] R. G. Meyer and W. D. Mack, "A 1-GHz BiCMOS RF front-end IC," *IEEE J. Solid-State Circuits*, vol. 29, pp. 350–355, Mar. 1994.

- [18] A. Rofougaran, G. Chang, J. Rael, J. Chang, M. Rofougaran, P. Chang, M. Djafari, J. Min, E. Roth, A. Abidi, and H. Samuels, "A single-chip 900-MHz spread-spectrum wireless transceiver in  $1\text{-}\mu\text{m}$  CMOS—Part II: Receiver design," *IEEE J. Solid-State Circuits*, vol. 33, pp. 535–547, Apr. 1998.

- [19] D. K. Shaeffer, A. Shahani, S. Mohan, H. Samavati, H. Rategh, M. del Mar Hershenson, X. Min, C. Yue, D. J. Eddleman, and T. H. Lee, "A 115-mW,  $0.5\text{-}\mu\text{m}$  CMOS GPS receiver with wide dynamic-range active filters," *IEEE J. Solid-State Circuits*, vol. 33, pp. 2219–2231, Dec. 1998.

- [20] P. Leroux, J. Janssens, and M. Steyaert, "A 0.8 dB NF ESD-protected 9 mW CMOS LNA," in *Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 2001, pp. 410–411.

- [21] A. N. Karanicolas, "A 2.7 V 900 MHz CMOS LNA and mixer," in *Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 1996, pp. 50–51.

- [22] A. Rofougaran, J. Y.-C. Chang, M. Rofougaran, and A. A. Abidi, "A 1 GHz CMOS RF front-end IC for a direct-conversion wireless receiver," *IEEE J. Solid-State Circuits*, vol. 31, pp. 880–889, July 1996.

- [23] D. K. Shaeffer and T. H. Lee, "A 1.5-V, 1.5-GHz CMOS low noise amplifier," *IEEE J. Solid-State Circuits*, vol. 32, pp. 745–759, May 1997.

- [24] R. E. Lehmann and D. D. Heston, "X-band monolithic series feedback LNA," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 1560–1566, Dec. 1985.

- [25] A. A. Abidi, G. J. Pottie, and W. J. Kaiser, "Power-conscious design of wireless circuits and systems," *Proc. IEEE*, vol. 88, pp. 1528–1545, Oct. 2000.

- [26] M. J. Strutt and A. Van der Ziel, "Suppression of spontaneous fluctuations in amplifiers and receivers for electrical communication and for measurement devices," *Physica*, vol. IX, no. 6, pp. 513–527, June 1942.

- [27] L. Besser, "Stability considerations of low-noise transistor amplifiers with simultaneous noise and power match," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1975, pp. 327–329.

- [28] H. A. Haus and R. B. Adler, "Optimum noise performance of linear amplifiers," *Proc. IRE*, pp. 1517–1533, Aug. 1958.

- [29] H. Fukui, "Available power gain, noise figure and noise measure of two-ports and their graphical representation," *IEEE Trans. Circuits Theory*, vol. CT-13, pp. 137–142, June 1966.

- [30] R. S. Tucker, "Low-noise design of microwave transistor amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-23, pp. 697–700, Aug. 1975.

- [31] J. Engberg, *Noise Theory of Linear and Nonlinear Circuits*. New York: Wiley, 1995.

- [32] D. M. Pozar and S. M. Duffy, "A dual-band circularly polarized aperture-coupled stacked microstrip antenna for global positioning satellite," *IEEE Trans. Antennas Propagat.*, vol. 45, pp. 1618–1625, Nov. 1997.

- [33] Z. D. Liu, P. S. Hall, and D. Wake, "Dual-frequency planar inverted-F antenna," *IEEE Trans. Antennas Propagat.*, vol. 45, pp. 1451–1458, Oct. 1997.

- [34] L. Zaid, G. Kossiavas, J. Dauvignac, J. Cazajous, and A. Papiermik, "Dual-frequency and broad-band antennas with stacked quarter wavelength elements," *IEEE Trans. Antennas Propagat.*, vol. 47, pp. 654–660, Apr. 1999.

- [35] H. Miyake, S. Kitazawa, T. Ishizaki, T. Yamada, and Y. Nagatomi, "A miniaturized monolithic dual band filter using ceramic lamination technique for dual mode portable telephones," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.*, 1997, pp. 789–792.

- [36] A. Nagayama, M. Nishibe, T. Inaoka, and N. Mineshima, "Low-insertion-loss DP3T MMIC switch for dual-band cellular phones," *IEEE J. Solid-State Circuits*, vol. 34, pp. 1051–1055, Aug. 1999.

- [37] A. de Graauw, C. Copetti, and W. Weekamp, "A new thin film passive integration technology for miniaturization of mobile phone front end modules: Integration of a dual-band power amplifier, switch and diplexer for GSM," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.*, vol. 3, 2000, pp. 1925–1928.

- [38] J. W. Archer, J. Granlund, and R. E. Mauzy, "A broad-band VHF mixer exhibiting high image rejection over a multidecade baseband frequency range," *IEEE J. Solid-State Circuits*, vol. SC-16, pp. 385–392, Aug. 1981.

- [39] J. C. Rudell, J.-J. Ou, T. B. Cho, G. Chien, F. Brianti, J. A. Weldon, and P. R. Gray, "A 1.9-GHz wide-band IF double conversion CMOS receiver for cordless telephone applications," *IEEE J. Solid-State Circuits*, vol. 32, pp. 2071–2088, Dec. 1997.

- [40] D. K. Weaver, "A third method of generation and detection of single-sideband signals," *Proc. IRE*, vol. 44, pp. 1703–1705, Dec. 1956.

- [41] K. L. Fong, "Dual-band high-linearity variable-gain low-noise amplifiers for wireless applications," in *Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 1999, pp. 224–225.

- [42] J. Rynnanen, K. Kivekas, J. Jussila, A. Parssinen, and K. Halonen, "A dual-band RF front-end for WCDMA and GSM applications," in *Proc. IEEE Custom Integrated Circuits Conf.*, May 2000, pp. 175–178.

- [43] R. Magoor, I. Koulias, L. Steigerwald, W. Domino, N. Vakilian, E. Ngompe, M. Damgaard, K. Lewis, and A. Molnar, "A triple-band 900/1800/1900MHz low-power image-reject front-end for GSM," in *Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 2001, pp. 408–409.

- [44] J. Janssens, J. Crols, and M. Steyaert, "A 10 mW inductorless, broadband CMOS low noise amplifier for 900 MHz wireless communications," in *Proc. IEEE Custom Integrated Circuits Conf.*, May 1998, pp. 75–78.

- [45] D. M. Pozar, *Microwave Engineering*, 2nd ed. New York: Wiley, 1998.

- [46] "IRE standards on electron tubes: Definition of terms," *Proc. IRE*, vol. 45, pp. 983–1010, July 1957. 57 IRE 7.S2.

- [47] A. Bellomo, "Gain and noise considerations in RF feedback amplifier," *IEEE J. Solid-State Circuits*, pp. 290–294, Sept. 1968.

- [48] A. van der Ziel, *Noise*. Englewood Cliffs, NJ: Prentice-Hall, 1954.

- [49] H. Rothe and W. Dahlke, "Theory of noisy fourpoles," *Proc. IEEE*, pp. 811–818, June 1956.

- [50] A. van der Ziel, *Noise in Solid State Devices and Circuits*. New York: Wiley, 1986.

- [51] A. A. Abidi, "High-frequency noise measurement on FET's with small dimensions," *IEEE Trans. Electron Devices*, vol. ED-33, pp. 1801–1805, Nov. 1986.

- [52] R. P. Jindal, "Hot-electron effects on channel thermal noise in fine-line NMOS field-effect transistors," *IEEE Trans. Electron Devices*, vol. ED-33, pp. 1395–1397, Sept. 1986.

- [53] A. Hajimiri, S. Limotyakis, and T. H. Lee, "Jitter and phase noise in ring oscillators," *IEEE J. Solid-State Circuits*, vol. 34, pp. 790–804, June 1999.

- [54] H. Fukui, "The noise performance of microwave transistor," *IEEE Trans. Electron Devices*, vol. ED-13, pp. 329–341, Mar. 1966.

- [55] J. Colvin and K. K. O, "Effects of substrate resistance on LNA performance and bondpad structure for reducing the effects in a silicon bipolar technology," *IEEE J. Solid-State Circuits*, vol. 34, pp. 1139–1344, Sept. 1999.

- [56] H. Tsui and J. Lau, "SPICE simulation and tradeoffs of CMOS LNA performance with source-degeneration inductor," *IEEE Trans. Circuits Syst. II*, vol. 47, pp. 62–65, Jan. 2000.

- [57] J. Janssens and M. Steyaert, "Optimum MOS power matching by exploiting nonquasistatic effect," *Electron. Lett.*, vol. 35, no. 8, pp. 672–673, Apr. 1999.

- [58] J. C. Greene, "Noisemanship—The art of measuring noise figures nearly independent of device performance," *Proc. IRE*, pp. 1223–1224, July 1961.

- [59] H. Samavati, H. R. Rategh, and T. H. Lee, "A 5-GHz CMOS wireless LAN receiver front end," *IEEE J. Solid-State Circuits*, vol. 35, pp. 765–772, May 2000.

- [60] R. G. Meyer and A. K. Wong, "Blocking and desensitization in RF amplifiers," *IEEE J. Solid-State Circuits*, vol. 30, pp. 944–946, Aug. 1995.

- [61] D. K. Shaeffer, "The design and implementation of low-power CMOS radio receivers." Ph.D. dissertation, Dept. Elect. Eng., Stanford Univ., Stanford, CA, Dec. 1998.

- [62] B. G. Choi, Y. S. Lee, C. S. Park, and K. S. Yoon, "Super low noise amplifier with minimum input matching network," *Electron. Lett.*, vol. 36, no. 19, pp. 1627–1629, Sept. 2000.

- [63] K. Kobayashi, A. Oki, L. Tran, and D. Streit, "Ultra-low power dc power GaAs HBT S- and C-band low noise amplifiers for portable wireless applications," *IEEE Trans. Microwave Theory Tech.*, vol. 43, pp. 3055–3061, Dec. 1995.

- [64] F. Ellinger, "A 5.2 GHz variable gain LNA MMIC for adaptive antenna combining," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.*, vol. 3, 1999, pp. 501–504.

- [65] U. Erben, H. Schumacher, A. Schuppen, and J. Arndt, "Application of SiGe heterojunction bipolar transistors in 5.8 and 10 GHz low-noise amplifiers," *Electron. Lett.*, vol. 34, no. 15, pp. 1498–1500, July 1998.

- [66] F. Behbahani, J. C. Leete, Y. Kishigami, A. Roithmeier, K. Hoshino, and A. A. Abidi, "A 2.4-GHz low-IF receiver for wideband WLAN in 6 $\mu$ m CMOS-architecture and front-end," *IEEE J. Solid-State Circuits*, vol. 35, pp. 1908–1916, Dec. 2000.

- [67] T. Liu and E. Westerwick, "5-GHz CMOS radio transceiver front-end chipset," *IEEE J. Solid-State Circuits*, vol. 35, pp. 1927–1933, Dec. 2000.

**Hossein Hashemi** (S'99) received the B.S. and M.S. degrees in electronics engineering from the Sharif University of Technology, Tehran, Iran, in 1997 and 1999, respectively, the M.S. degree in electrical engineering from the California Institute of Technology (Caltech), Pasadena, in 2001, and is currently working toward the Ph.D. degree at Caltech.

His research interest is mainly focused on high-speed and RF integrated circuits.

Mr. Hashemi was the recipient of the 1999 Caltech Engineering and Applied Science Division Fellowship Award, the 2000 Walker von Brimer Foundation Outstanding Accomplishment Award, and the 2001 Analog Devices Outstanding Student Designer Award.

**Ali Hajimiri** (S'94–M'98) received the B.S. degree in electronics engineering from the Sharif University of Technology, Tehran, Iran, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1996 and 1998, respectively.

From 1993 to 1994, he was a Design Engineer with Philips Semiconductors, where he was involved with a BiCMOS chipset for GSM and cellular units. In 1995, he was with Sun Microsystems, where he was involved with the UltraSPARC microprocessor's cache RAM design methodology. During

the summer of 1997, he was with Lucent Technologies (Bell Laboratories), Holmdel, NJ, where he investigated low-phase-noise integrated oscillators. In 1998, he joined the Faculty of the California Institute of Technology, Pasadena, as an Assistant Professor of electrical engineering, where his research interests are high-speed and RF integrated circuits. He co-authored *The Design of Low Noise Oscillators* (Norwell, MA: Kluwer, 1999) and holds several U.S. and European patents.

Dr. Hajimiri is a member of the Technical Program Committees of the International Conference on Computer-Aided Design (ICCAD). He was the recipient of the Gold Medal of the National Physics Competition and the Bronze Medal of the 21st International Physics Olympiad, Groningen, The Netherlands. He was a corecipient of the International Solid-State Circuits Conference 1998 Jack Kilby Outstanding Paper Award and the recipient of the IBM Faculty Partnership Award. He was a guest editor for the *IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES*.